MIMD

| Одиночний потік інструкцій Single Instruction | Множинний потік інструкцій Multiple Instruction | |

| Одиночний потік даних Single Data | SISD | MISD |

| Множинний потік даних Multiple Data | SIMD | MIMD |

Цей шаблон:

| ||

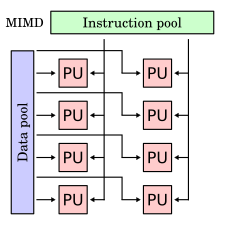

MIMD (англ. multiple instruction, multiple data — множинний потік команд, множинний потік даних) — це елемент класифікації згідно з таксономією Флінна для паралельних процесорів, де є декілька обчислювальних пристроїв обробки команд, кожен з яких працює зі своїм набором команд.

Типологія паралельних (MIMD) архітектур (за доступом до пам'яті)

Усі процесори мають бути об'єднані за допомогою швидкісної локальної мережі, це необхідно для взаємодії між процесорами.

З розподіленою пам'яттю (Distributed memory)

У даній моделі присутні лише процесори і кеш між ними. Кожен процесор у системі має доступ лише до своєї локальної пам'яті. Також окрім обчислення процесор може відсилати і отримувати дані з мережі, саме за допомогою повідомлень і відбувається обмін даними між процесорами. В ідеальній мережі вартість пересилання даних між двома процесорами не залежить від їх розташування у мережі, а залежить лише від довжини повідомлення.

Усі процесори спільно звертаються до загальної пам'яті, як правило, через шину чи ієрархію шин. В ідеалізованої PRAM (Parallel Random Access Machine — паралельна машина з довільним доступом) моделі, яка часто використовується в теоретичних дослідженнях паралельних алгоритмів, будь-який процесор може звертатися до будь-якої комірки пам'яті у той самий час.

У таких комп'ютерах загальна пам'ять відсутня. Процесор може використовувати як свою локальну пам'ять так і пам'ять інших процесорів, за допомогою «глобальної адреси». У випадку якщо глобальна адреса вказує не на локальну пам'ять, то доступ до пам'яті здійснюється за допомогою повідомлень, з малою затримкою, що пересилаються по мережі.

Посилання

- https://web.archive.org/web/20120118070349/http://www.itswtech.org/Lec/ameer(DCS4th)/lecture2.pdf

- http://www.cs.umd.edu/class/fall2001/cmsc411/projects/MIMD/mimd.html [Архівовано 31 грудня 2012 у Wayback Machine.]

- http://www.ccas.ru/paral/mimd/mimd.html [Архівовано 9 травня 2013 у Wayback Machine.]

| ||||||||||||||||||||||||||||||||

| Ця стаття потребує додаткових посилань на джерела для поліпшення її перевірності. Будь ласка, допоможіть удосконалити цю статтю, додавши посилання на надійні (авторитетні) джерела. Зверніться на сторінку обговорення за поясненнями та допоможіть виправити недоліки. Матеріал без джерел може бути піддано сумніву та вилучено. (січень 2016) |

| Це незавершена стаття про апаратне забезпечення. Ви можете допомогти проєкту, виправивши або дописавши її. |