Nehalem (microarquitectura)

Nehalem (microarquitectura) Nehalem (microarquitectura) | |

|---|---|

| |

| Característiques de CPUs | |

| Conjunt d'instruccions | x86-64 |

← Intel Core (microarquitectura)  Sandy Bridge  → → | |

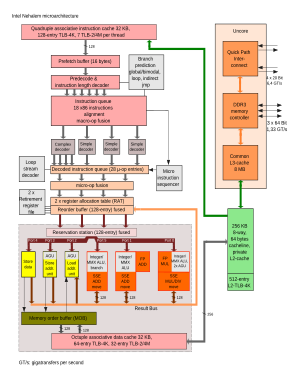

Nehalem /nəˈheɪləm/ és el nom en clau de la microarquitectura de 45 nm d'Intel publicada el novembre de 2008. Es va utilitzar a la primera generació dels processadors Intel Core i5 i i7, i succeeix l'antiga microarquitectura Core utilitzada en els processadors Core 2. El terme "Nehalem" prové del riu Nehalem.[1]

Nehalem es basa en el procés de 45 nm, és capaç de funcionar a velocitats de rellotge més altes sense escarificar l'eficiència i és més eficient energèticament que els microprocessadors Penryn. Es reintrodueix l'hiper-threading, juntament amb una reducció de la mida de la memòria cau L2, així com una memòria cau L3 ampliada que es comparteix entre tots els nuclis. Nehalem és una arquitectura que difereix radicalment de NetBurst, tot i que conserva algunes de les característiques menors d'aquest últim.[2]

Més tard, Nehalem va rebre una reducció a 32 nm amb Westmere, i el Sandy Bridge de "segona generació" el va succeir completament el gener de 2011.[3]

Tecnologia [4]

- El bloc de línies de memòria cau a la memòria cau L2/L3 es va reduir de 128 bytes a NetBurst i Merom/Penryn a 64 bytes per línia en aquesta generació (la mateixa mida que Yonah i Pentium M).

- Hiper-threading reintroduït.

- Intel Turbo Boost 1.0.

- 2–24 Memòria cau MiB L3 amb Smart Cache en alguns models.

- Unitat d'obtenció d'instruccions (IFU) que conté un predictor de branca de segon nivell amb dos nivells de memòria intermèdia de destí de branca (BTB) i buffer de pila de retorn (RSB). Nehalem també admet tots els tipus de predictors utilitzats anteriorment als processadors d'Intel, com ara el predictor indirecte i el detector de bucles.

- sTLB (búfer de traducció unificada de segon nivell) (és a dir, tant instruccions com dades) que conté 512 entrades només per a pàgines petites, i de nou és associatiu de 4 vies.

- 3 ALU enters, 2 ALU vectorials i 2 AGU per nucli.

- Processadors nadius (tots els nuclis del processador en una sola matriu) de quatre nuclis, hexadecimals i octacores

- Intel QuickPath Interconnect en models HEDT, servidor i estació de treball i Direct Media Interface en altres models que substitueixen el bus frontal heretat.

- 64 Memòria cau L1 KB per nucli (32 Dades KB L1 i 32 Instrucció KB L1) i 256 Memòria cau L2 KB per nucli.

- Integració de PCI Express i DMI al processador en models de gamma mitjana, substituint el Northbridge.

- Controlador de memòria integrat que admet dos o tres canals de memòria de DDR3 SDRAM o quatre canals FB-DIMM2.

- Tecnologia de virtualització Intel de segona generació, que va introduir suport de taula de pàgines ampliada, identificadors de processadors virtuals (VPID) i sortida de finestra d'interrupció no emmascarable.

- Instruccions SSE4.2 i

POPCNT. - La fusió de macrooperacions ara funciona en mode de 64 bits.

- De 20 a 24 etapes de canonada.

Referències

- ↑ «How the Nehalem Microprocessor Microarchitecture Works» (en anglès americà), 15-01-2009. [Consulta: 3 gener 2024].

- ↑ Makar, A. B.; McMartin, K. E.; Palese, M.; Tephly, T. R. «Formate assay in body fluids: application in methanol poisoning». Biochemical Medicine, 13, 2, 1975-06, pàg. 117–126. DOI: 10.1016/0006-2944(75)90147-7. ISSN: 0006-2944. PMID: 1.

- ↑ «[https://www.intel.com/pressroom/archive/reference/whitepaper_Nehalem.pdf 1 First the Tick, Now the Tock: Next Generation Intel® Microarchitecture (Nehalem)]» (en anglès). [Consulta: 3 gener 2024].

- ↑ Stokes, Jon. «What you need to know about Intel's Nehalem CPU» (en anglès americà), 09-04-2008. [Consulta: 3 gener 2024].